Quelque chose à espérer: L’évolution des technologies et des exigences de traitement d’aujourd’hui a poussé les fabricants de puces à rechercher des conceptions alternatives qui s’écartent des architectures monolithiques standard à base de puces. Plus tôt cette semaine, Taiwan Semiconductor Manufacturing Company (TSMC) a annoncé la formation de la 3D Fabric Alliance pour mieux répondre à ces exigences. L’Alliance crée un effort de collaboration entre les partenaires de l’industrie pour accélérer la conception, le développement et l’adoption de produits basés sur des puces 2.5D et 3D.

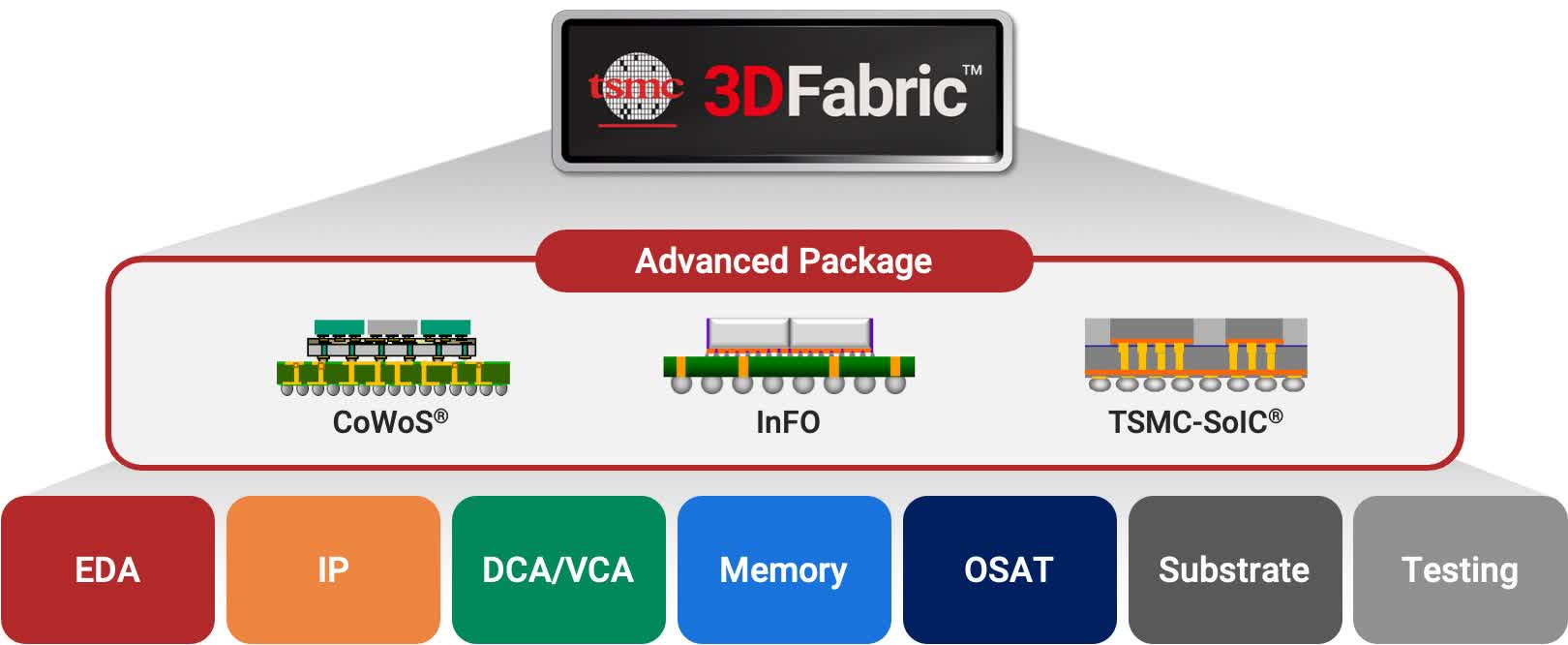

La 3DFabric Alliance applique l’expertise combinée de plusieurs partenaires industriels pour créer et affiner les technologies de conception et d’emballage basées sur les puces. L’alliance de 19 membres, qui devrait s’étendre, couvre l’ensemble de l’écosystème de produits et comprend des partenaires spécialisés dans la conception, l’automatisation, la mémoire, les substrats, les tests et d’autres domaines du processus de fabrication. Ces membres travailleront ensemble pour développer Spécifications de la technologie 3DFabric selon les règles et normes établies par TSMC.

L’Alliance fait partie de la plus grande plateforme d’innovation ouverte (OIP) de TSMC. Le modèle OIP fournit un moyen pour les clients et les partenaires de l’industrie de collaborer et d’établir de nouvelles approches pour raccourcir le temps de conception des circuits intégrés (CI). Il vise également à améliorer le délai de production de volume, le délai de mise sur le marché et le délai de génération de revenus.

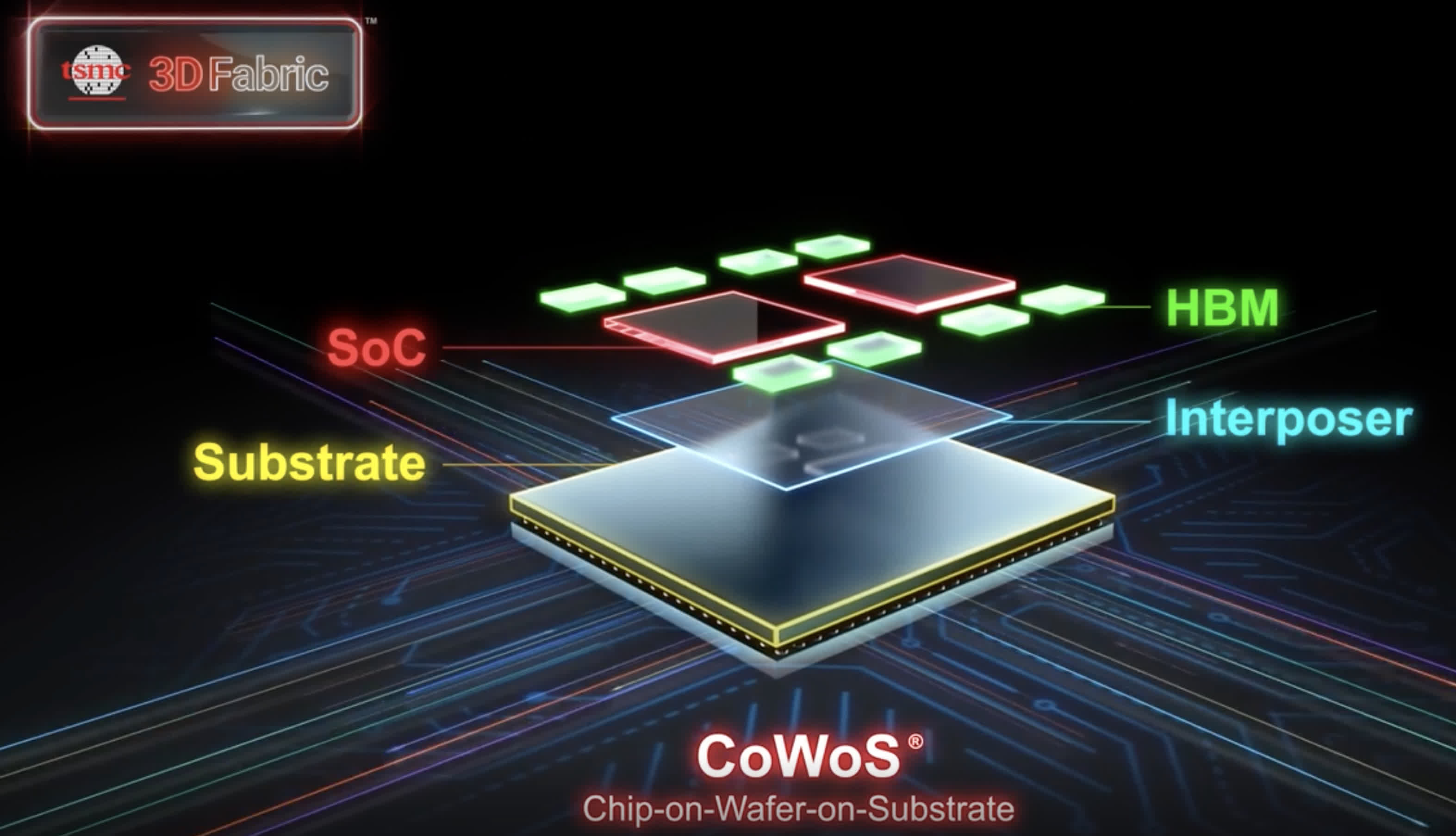

3DFabric de Taiwan Semiconductor Manufacturing Company est une famille de technologies d’interconnexion front-end et back-end conçues pour augmenter la puissance de calcul future et le nombre de cœurs, augmenter les plafonds de mémoire et de bande passante et améliorer la fourniture d’énergie globale. L’approche prend en charge le système de TSMC sur les services de puce intégrés, y compris puce sur plaquette et plaquette sur plaquette méthodologies d’empilage de matrices. Cette technique utilise un empilement vertical haute densité pour augmenter les performances et réduire la consommation d’énergie. Il permet également une meilleure intégration de bonnes puces connues avec des puces de différentes tailles et fonctionnalités, améliore l’évolutivité globale et réduit l’encombrement et le profil de la puce.

L’objectif primordial de l’Alliance 3DFabric est de créer des solutions standard et interopérables qui accélèrent les efforts de conception et de développement de puces multiples pour une utilisation dans tous les secteurs. Selon TSMC, le rôle des semi-conducteurs continuera d’augmenter dans tous les secteurs en raison de leur utilisation dans tous les domaines, de la conception et de la fabrication automobiles aux centres de données et aux appareils intelligents. La capacité de 3DFabric Alliance à optimiser et à rationaliser la conception, le développement et la mise en œuvre contribuera à garantir des innovations continues pour la technologie des semi-conducteurs et les produits et services quotidiens qui en dépendent.