La grande image: TSMC progresse sur ses plans de nœuds de processus 3 nm (N3), N3E entrant en production en volume plus tard cette année. La société vient de voir ses revenus baisser pour la première fois en quatre ans, mais elle va de l’avant avec d’importantes dépenses de R&D pour s’assurer que ses nœuds de classe 2 nm seront prêts avant qu’Intel et d’autres ne puissent rattraper leur retard.

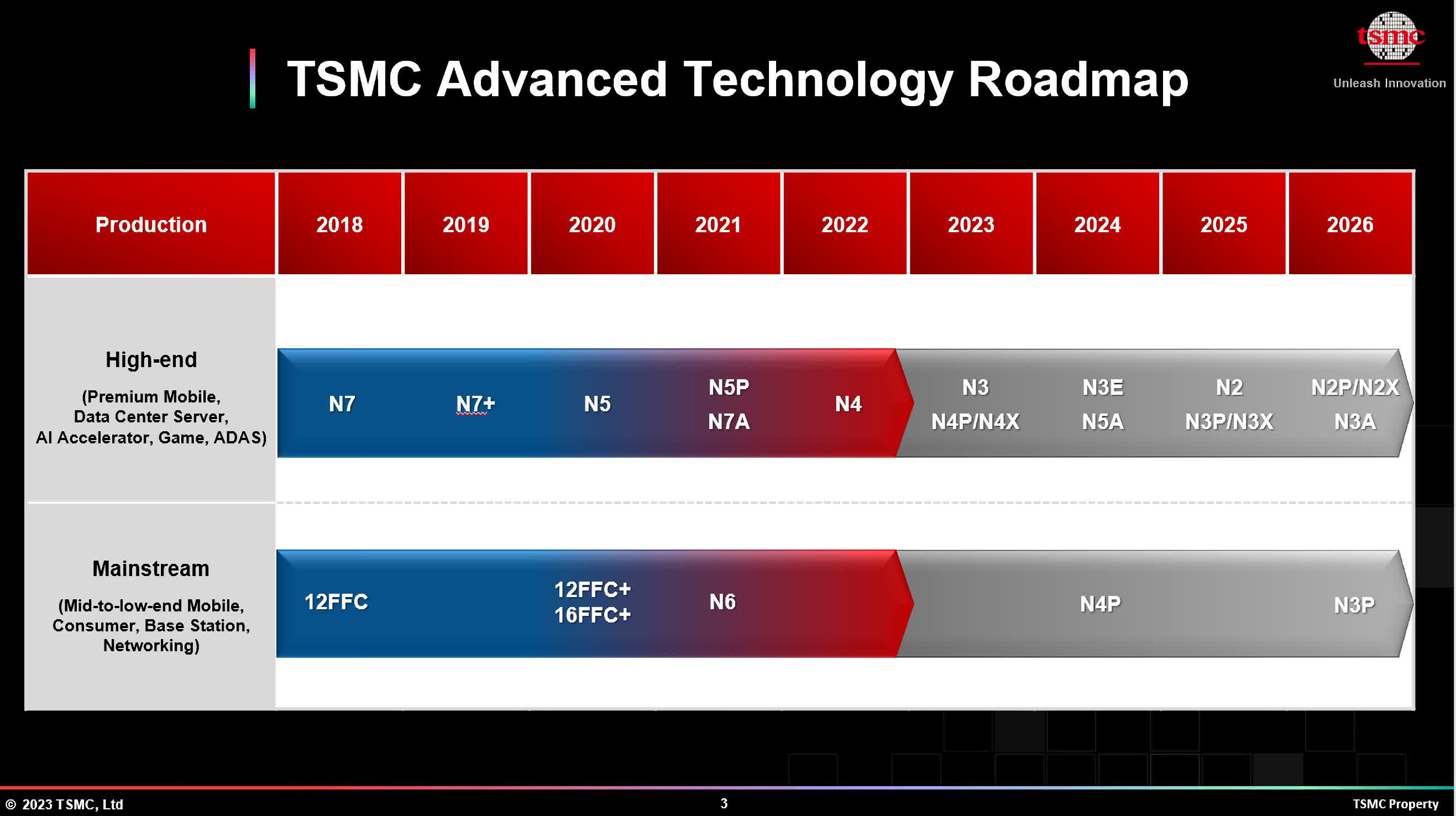

Cette semaine, TSMC a présenté certaines des principales caractéristiques de ses technologies de nœuds de processus actuelles et futures lors du North America Technology Symposium 2023 à Santa Clara, en Californie. La feuille de route de la société taïwanaise comprend une gamme de nouvelles technologies de silicium pour divers besoins de l’industrie qui s’étend jusqu’en 2026, et pas moins de 1 600 partenaires et clients participent à l’événement.

Actuellement, TSMC utilise la technologie 3 nm (N3) dans la fabrication en série – la plupart pour le silicium Apple – et un nœud N3E devrait démarrer la production au second semestre de cette année. Les avantages de N3 incluent une amélioration de la vitesse de 18 % à la même puissance que N5, avec une densité logique approchant 1,6 fois celle de l’ancien nœud. Il est également moins complexe (et donc moins coûteux) à utiliser que le N3 car il ne nécessite pas de double motif EUV pour obtenir les améliorations de densité revendiquées.

À partir de l’année prochaine, TSMC étend son portefeuille 3 nm avec trois nouveaux nœuds : N3P, N3X et N3AE. Le N3P est un raffinement du N3E dans le but d’augmenter encore la densité des transistors tout en offrant des performances supérieures de cinq pour cent à la même puissance ou une efficacité énergétique supérieure de cinq à dix pour cent aux mêmes horloges. Et comme il ne s’agit que d’un rétrécissement optique de N3E, les conceptions basées sur N3P seront compatibles avec l’avenir, ce qui signifie que N3P sera probablement un choix populaire parmi les entreprises de conception de puces.

Le N3X est conçu avec un calcul haute performance à l’esprit, ce sera donc un choix attrayant pour des éléments tels que les processeurs, les GPU et les accélérateurs d’IA. Cela permettra d’obtenir des vitesses d’horloge supérieures d’au moins cinq pour cent par rapport à N3P au prix de courants de fuite plus élevés (et nécessitant donc des tensions plus élevées pour la stabilité). TSMC indique que N3X prendra en charge des tensions d’environ 1,2 volts, ce qui signifie que ce nœud sera le plus utile pour le matériel de qualité serveur avec des systèmes de refroidissement puissants.

TSMC prévoit d’avoir N3P en production de masse au cours du second semestre 2024, tandis que N3X ne sera pas prêt avant 2025. Les initiés de la chaîne d’approvisionnement affirment que les GPU Celestial d’Intel seront parmi les premiers à utiliser ce dernier nœud, mais nous devrons attend et regarde. Quant au N3AE, il s’agit d’un nœud optimisé pour les puces utilisées dans les applications automobiles qui sera également disponible pour les constructeurs automobiles en 2025.

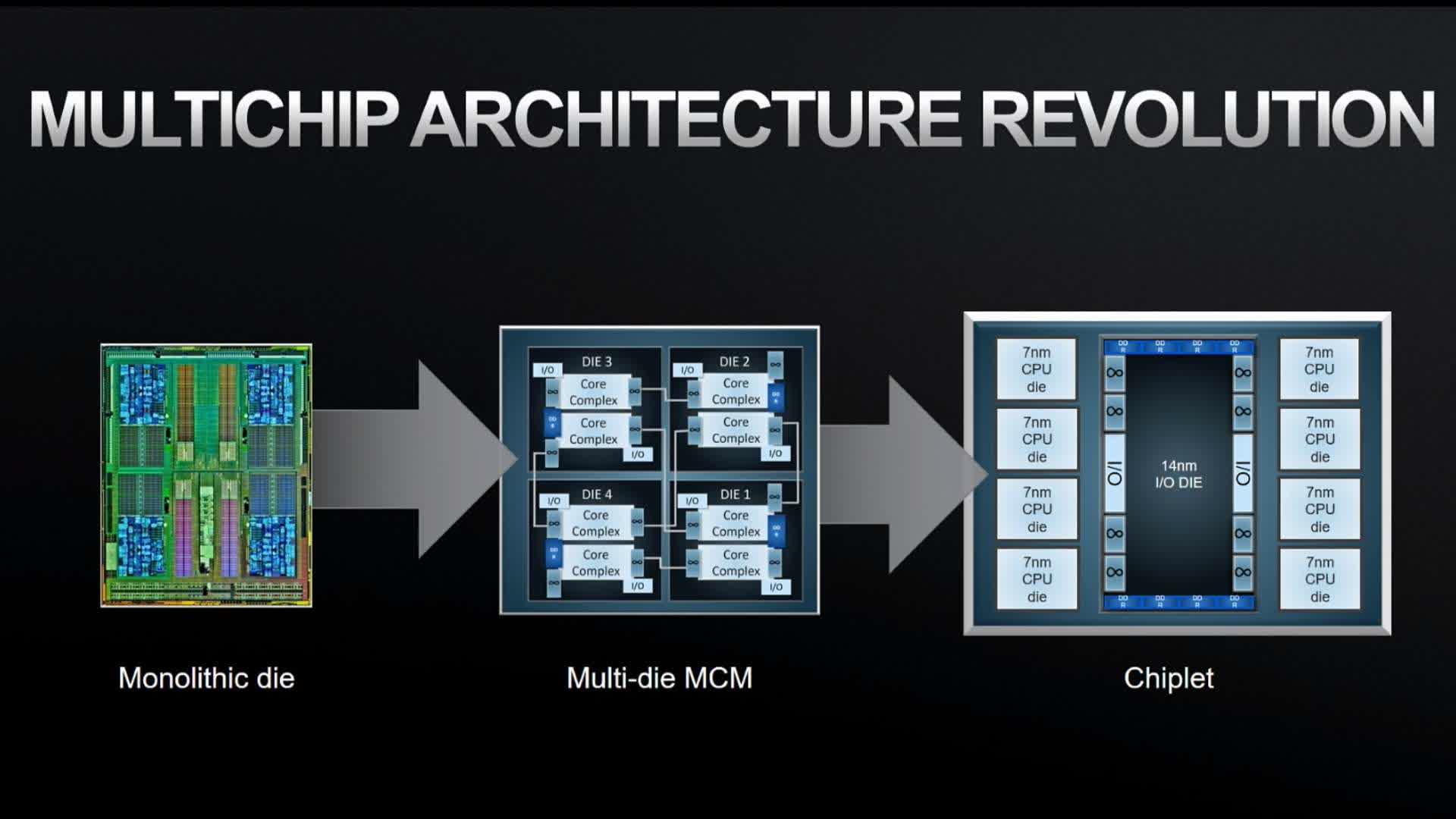

Une chose est sûre – les nœuds de classe N3 accéléreront le développement d’architectures basées sur des puces (le RDNA 3 d’AMD me vient à l’esprit) avec des matrices de calcul fabriquées sur le nœud le plus récent et le plus grand et une mémoire supplémentaire et des matrices d’E/S fabriquées à l’aide de nœuds plus matures avec une meilleure rentabilité et des rendements plus prévisibles.

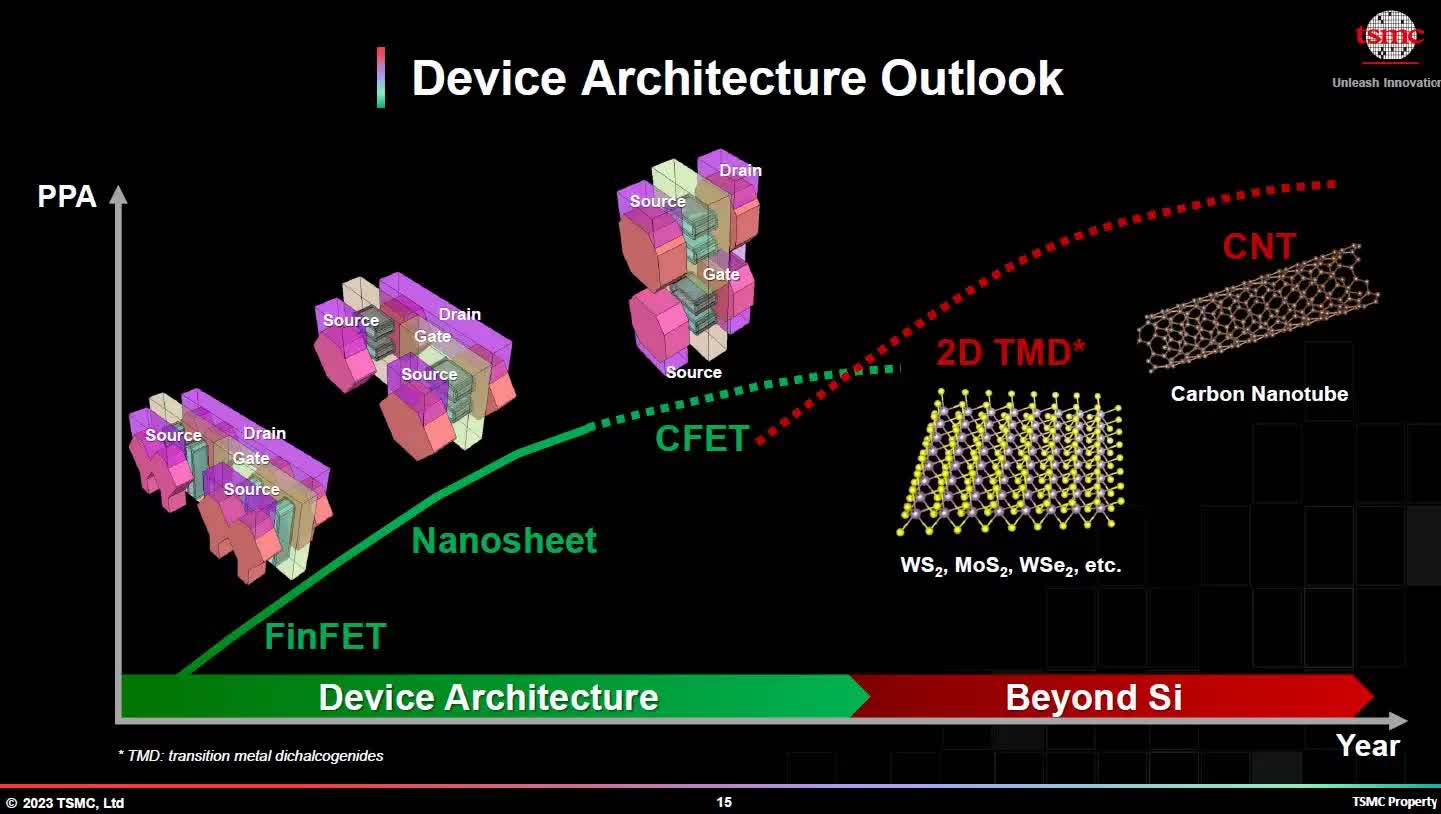

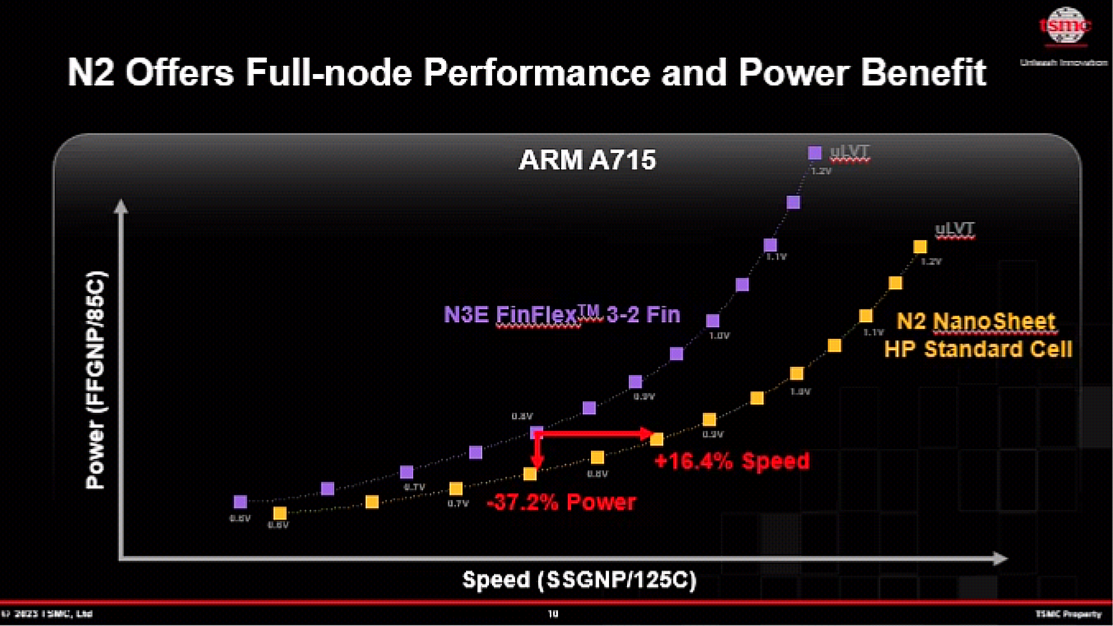

La société a également présenté une feuille de route pour les nœuds de processus de 2 nm (N2), qui intègrent des transistors « nanosheet » (alias gate-all-around ou GAAFET) et permettent des performances, une efficacité énergétique et des densités de transistors encore meilleures pour la logique, la SRAM et circuits analogiques. Un avantage par rapport aux transistors FinFET existants est un courant de fuite plus faible, et un autre est que la largeur de canal peut être ajustée pour des performances plus élevées ou une consommation d’énergie plus faible.

Sinon, TSMC affirme que N2 offrira 10 à 15% de performances supplémentaires à la même puissance que N3 ou une réduction de puissance de 25 à 20% aux mêmes horloges. La société est également optimiste quant à la possibilité d’atteindre des densités de puces mixtes (SRAM, logique et analogique) avec N2 supérieures de plus de 15 % à celles de N3E.

Quant à l’état d’avancement du processus de développement, les nouveaux transistors à nanofeuilles répondent déjà à 80 % des spécifications de performances cibles, tandis que le rendement moyen d’une SRAM de 256 Mo oscille actuellement juste au-dessus de 50 %. Avec une production à haut volume prévue pour 2025, l’entreprise a tout le temps d’améliorer ces chiffres.

La famille N2 s’agrandira en 2026 avec N2P, qui ajoutera une alimentation électrique arrière. Tout comme le PowerVia d’Intel et le BSPDN de Samsung, l’idée est de placer les transistors entre le réseau d’alimentation et le réseau de signal, améliorant ainsi les performances des transistors et réduisant ainsi la consommation d’énergie.

Cela peut ne pas sembler beaucoup, mais les réseaux de distribution d’énergie arrière font partie des innovations les plus importantes dans le domaine des semi-conducteurs ces dernières années. Il modifie la manière dont l’énergie est fournie aux transistors sur une puce d’une manière qui améliore l’efficacité énergétique et offre des améliorations significatives de la densité logique. Selon les estimations d’Applied Materials, la fourniture d’énergie par l’arrière permet des réductions de surface de cellule logique de 20 à 30 pour cent – l’équivalent de deux générations de lithographie à améliorer.

N2P ne sera pas prêt pour la fabrication en série avant 2026 et TSMC n’a pas encore fourni de chiffres sur sa comparaison avec N2. C’est une histoire similaire avec N2X, la variante conçue pour le calcul haute performance où les tensions et les horloges sont poussées au point de rendements décroissants.

Au contraire, Intel a une fenêtre d’opportunité pour rattraper TSMC avec les nœuds Intel 20A et 18A, le premier devant entrer en production en volume fin 2024. Cependant, étant donné les mauvais antécédents d’Intel en matière de livraison dans les délais et les difficultés de sécurisant les équipements EUV ASML de pointe, nous ne nous attendons à aucun miracle.