Pourquoi est-ce important: Un article intéressant publié sur Puce Wiki traite de la gravité des problèmes de rétrécissement de SRAM dans l’industrie des semi-conducteurs. Le fabricant TSMC rapporte que la mise à l’échelle de ses transistors SRAM s’est complètement stabilisée au point où les caches SRAM restent de la même taille sur plusieurs nœuds, malgré la diminution continue des densités de transistors logiques. Ce n’est pas idéal et cela obligera les caches SRAM du processeur à occuper plus d’espace sur une puce à puce. Cela pourrait à son tour augmenter les coûts de fabrication des puces et empêcher certaines architectures de micropuces de devenir aussi petites qu’elles pourraient l’être.

Presque tous les processeurs s’appuient sur une forme de mise en cache SRAM. Les caches agissent comme une solution de stockage à grande vitesse avec des temps d’accès très rapides en raison de leur emplacement stratégique juste à côté des cœurs de traitement. Disposer d’un stockage rapide et accessible peut augmenter considérablement les performances de traitement et réduire le temps perdu par les cœurs pour faire leur travail.

Lors de la 68e conférence annuelle IEEE International EDM, TSMC a révélé d’énormes problèmes avec la mise à l’échelle de la SRAM. Le prochain nœud de la société qu’elle développe pour 2023, N3B, inclura la même densité de transistors SRAM que son prédécesseur N5, qui est utilisé dans des processeurs comme la série Ryzen 7000 d’AMD.

Un autre nœud actuellement en développement pour 2024, N3E n’est pas tellement mieux, avec une maigre réduction de 5% de la taille des transistors SRAM…

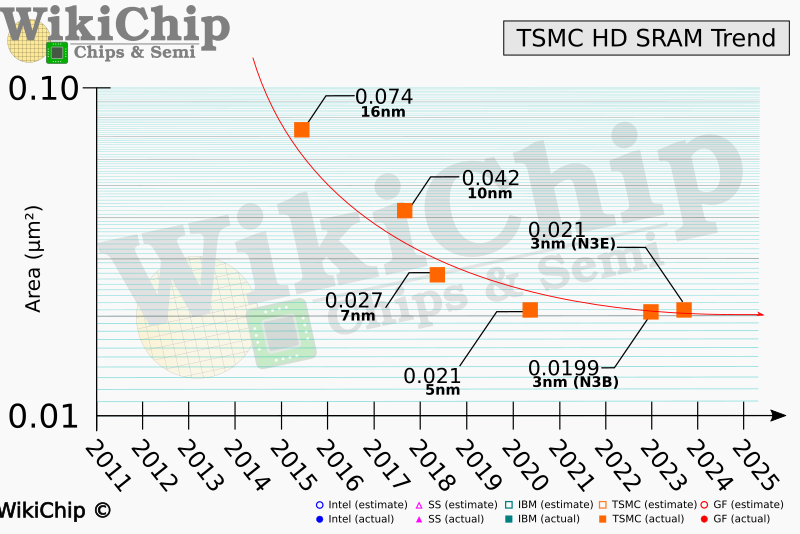

Pour une perspective plus large, WikiChip a partagé un graphique de l’historique de mise à l’échelle SRAM de TSMC de 2011 à 2025. La première moitié du graphique – représentant les jours 16 nm et 7 nm de TSMC – montre comment la mise à l’échelle SRAM n’était pas un problème et comment elle devenait plus petite à un rythme rapide. Mais une fois que le graphique atteint 2020, la mise à l’échelle est essentiellement plate, avec trois générations de nœuds logiques TSMC utilisant des tailles SRAM presque identiques : N5, N3B et N3E.

La densité des transistors logiques augmentant toujours à un rythme rapide – jusqu’à 1,7x dans le cas du N3E – mais sans la densité des transistors SRAM suivant le même chemin, la SRAM commencera à consommer beaucoup d’espace de matrice au fil du temps. Wikichip l’a démontré avec une hypothétique puce à transistors de 10 milliards, fonctionnant sur plusieurs nœuds. Sur N16 (16 nm), la matrice est grande avec seulement 17,6 % de la surface de la matrice composée de transistors SRAM, sur N5, cela monte à 22,5 % et 28,6 % sur N3.

WikiChip signale également que TSMC n’est pas le seul fabricant à rencontrer des problèmes similaires. Intel a également constaté des ralentissements notables dans le rétrécissement des transistors SRAM sur son processus Intel 4.

À moins que cela ne soit résolu d’une manière ou d’une autre, nous pourrions bientôt voir des caches SRAM consommer jusqu’à 40 % de l’espace de puce d’un processeur. Cela conduirait à retravailler les architectures de puces et à augmenter les coûts de développement. Une autre façon pour les fabricants de faire face est de réduire complètement la capacité du cache, ce qui réduirait les performances. Cependant, il existe des remplacements de mémoire alternatifs à l’étude, notamment MRAM, FeRAM et NRAM, pour n’en nommer que quelques-uns. Mais pour l’instant, cela reste un défi sans réponse claire dans l’immédiat.